Description

СБИС 1879ВМ6Я – высокопроизводительный процессор цифровой обработки сигналов. Архитектура процессора основывается на использовании нового поколения VLIW/SIMD процессорного ядра NMC4. Процессор содержит два процессорных ядра NMPU0 и NMPU1, каждое из которых включает RISC процессор и векторный сопроцессор. Первый 64-разрядный сопроцессор предназначен для выполнения векторно-матричных операций над целочисленными данными переменной длины от 1 до 64 разрядов. Второй 64-разрядный сопроцессор предназначен для векторных операций с плавающей точкой.

Состав процессора

Два процессорных ядра NMPU0, NMPU1

NMPU0 содержит RISC процессорное ядро с 32/64-разрядным сопроцессором плавающей точки

NMPU1 содержит RISC процессорное ядро с 64-разрядным сопроцессором векторно-матричных операций над целочисленными данными переменной длины от 1 до 64 разрядов

12 двухпортовых банков внутренней SRAM памяти (16Кx64 разряда каждый)

4 Мбит распределенной памяти

1Кх64 разряда кэш команд

32-разрядный интерфейс с внешней памятью DDR2 400 МГц

Четыре байтовых коммуникационных порта с пропускной способностью до 1 Гбит/с каждый

16 портов GPIO

JTAG контроллер и порт для отладки и тестирования

Два независимых ПДП контроллера

Контроллер внешних/внутренних прерываний

Двойной 32-разрядный таймер

Watch Dog таймер

SPI контроллер

USB2.0 OTG контроллер

Системный контроллер

ROM начальной загрузки

Асинхронные буфера

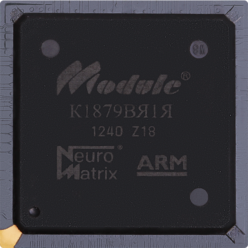

Основные характеристики

Технология – 65нм КМОП

Корпус – 544BGA

Память на кристалле – 16 Мбит

Частота синхронизации – 500 МГц

Напряжения источников питания – 1,0В (ядро), 1,8В (DDR2), 3,3В (буфера)

Типовая потребляемая мощность – 2,4 Вт

Максимальная потребляемая мощность – 7 Вт

Диапазон температуры окружающей среды: -45°C… +85°C

RISC процессор

Разрядность данных – 32 бита

Разрядность команд – 32 и 64 бита

Адресное пространство – 4Гх32 бит

3 скалярные инструкции за такт (АЛУ операция, операция модификации адреса, ввод/вывод)

Производительность – 1000 MIPS (3000 MOPS)

Векторно-матричный сопроцессор целочисленной арифметики

Программируемая длина данных от 2 до 64 бит (64 бит упакованная длина слова)

Базовая операция – целочисленное матричное умножение

Одновременное выполнение 2 функций насыщения

Производительность (МАС– Multiplication and Accumulation за такт):

- 2 MAC для 32-разрядных данных

- 4 MAC для 16-разрядных данных

- 24 MAC для 8-разрядных данных

- 80 MAC для 4-разрядных данных

- 224 MAC для 2-разрядных данных

Сопроцессор плавающей точки

Четыре вычислительных ячейки

Ячейка выполняет 8 операций одинарной точности или 2 операции двойной точности в формате плавающей точки за такт

Ячейка содержит 8 векторных 32х64 разрядных регистра

Переупаковщик данных из целочисленного в плавающий формат (и наоборот)

Производительность – 16 GFLOPS с данными одинарной точности

Применение

Обработка широкополосных радиолокационных сигналов, в том числе различные виды цифровой фильтрации, преобразования Фурье, Адамара и прочее

Обработка изображений (включая различные виды фильтрации и MPEG кодирование и декодирование)

Навигация

Высокопроизводительная коммутация сигналов

CDMA и TDMA базовые станции сотовой связи